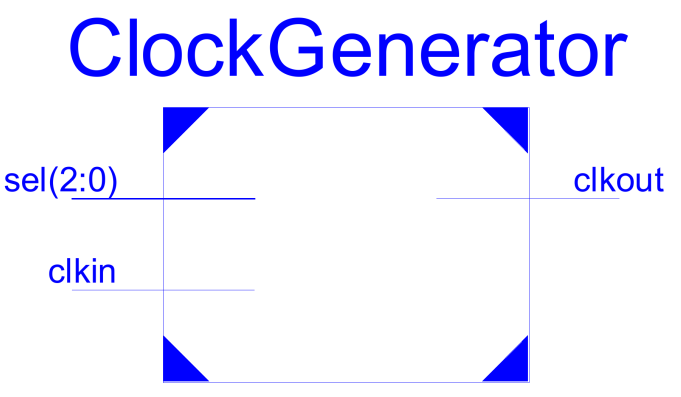

Programmable Clock Generator

Design and implement a Programmable Clock Generator.

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: EAM

// Create Date: 08:15:45 04/29/2015

// Module Name: ClockGenerator

// Project Name: Programmable Clock Generator

//////////////////////////////////////////////////////////////////////////////////

COUNTER

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

--------------------------------------------------------------------------------------------------------------

entity CNTR is

Port ( CLK : in STD_LOGIC;

CNT : out STD_LOGIC_VECTOR (4 downto 0));

end CNTR;

--------------------------------------------------------------------------------------------------------------

architecture Behavioral of CNTR is

signal Y: STD_LOGIC_VECTOR(4 downto 0):="00000";

begin

PROCESS (CLK)

begin

if (CLK='0' and CLK'event) then

Y<= Y+"00001";

end if;

end PROCESS;

CNT<=Y;

end Behavioral;

MAIN

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

--------------------------------------------------------------------------------------------------------------

entity EXP3 is

Port ( CLK : in STD_LOGIC;

SEL : in STD_LOGIC_VECTOR (2 downto 0);

CLK_OUT : out STD_LOGIC);

end EXP3;

--------------------------------------------------------------------------------------------------------------

architecture Behavioral of EXP3 is

component CNTR

Port ( CLK : in STD_LOGIC;

CNT : out STD_LOGIC_VECTOR (4 downto 0));

end component;

signal count:STD_LOGIC_VECTOR(4 DOWNTO 0) ;

begin

X1: CNTR port map(CLK, count);

process (CLK, SEL, count)

begin

case SEL is

when "000"=>

CLK_OUT<='0';

when "001"=>

CLK_OUT<=CLK;

when "010"=>

CLK_OUT<=count(0);

when "011"=>

CLK_OUT<=count(1);

when "100"=>

CLK_OUT<=count(2);

when "101"=>

CLK_OUT<=count(3);

when "110"=>

CLK_OUT<=count(4);

when "111"=>

CLK_OUT<='1';

when others=>

CLK_OUT<='Z';

end case;

end process;

end Behavioral;