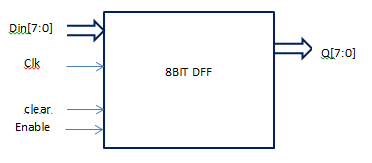

8BIT D FLIPFLOP

AIM:Design and implement an 8bit d-flipflop with enable input and synchronous clear.DESIGN

`timescale 1ns / 1ps

// Company: TMP

// Create Date: 08:15:45 01/12/2015

// Module Name: 8bit DFlipflop

// Project Name: 8bit DFlipflop

///////////////////////////////////////////////////////////////////////////

endmodule

.................................................................................................

Related Programs:

Verilog program for Basic Logic Gates

Verilog program for Half Adder

Verilog program for Full Adder

Verilog program for 4bit Adder

Verilog program for Half Substractor

Verilog program for Full Substractor

Verilog program for 4bit Substractor

Verilog program for Carry Look Ahead Adder

Verilog program for 3:8 Decoder

Verilog program for 8:3 Encoder

Verilog program for 1:8 Demultiplxer

Verilog program for 8:1 Multiplexer

Verilog program for 8bit D Flipflop

Verilog program for T Flipflop

Verilog program for JK Flipflop

Verilog program for Equality Comparator

Verilog program for 8bit Up down counter

Verilog program for 8bit Shift Register (SIPO,PISO,PIPO)

Verilog program for Random Access Memory(RAM)

Verilog program for Programmable clock Generator

Verilog program for Finite State Machine (mealy)

Verilog program for Finite State Machine (moore)